Контроллеры

крейта КАМАК K0607 и К0607М

Крейт-контроллер

К0607 предназначен для преобразования управляющих воздействий

ЭВМ в сигналы стандарта КАМАК, приема запросов от модулей

и передачи прерывания в ЭВМ. Крейт-контроллер устанавливается

всегда в крайнюю правую позицию крейта и занимает два места.

С компьютером контроллер соединен одним коаксиальным кабелем

75ом через интерфейс ППИ (Параллельно-Последовательный Интерфейс

в стандарте ISA) или ИПС (Интерфейс Последовательной Связи

в стандарте PCI). Максимальная длина соединительного кабеля

- до 200м, техническая скорость передачи информации 10 Мбит/сек.

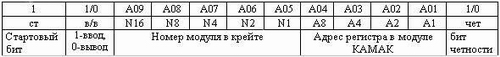

Любой обмен с контроллером начинается с 12-ти разрядной адресной

посылки. Взаимно - однозначное соответствие адресов регистров

блоков КАМАК и разрядов адресной посылки следующее:

При приеме посылки

с адресом модуля КАМАК, равным N(0), выполняется операция

с одним из внутренних регистров контроллера.

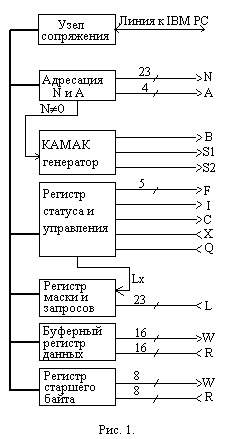

Устройство контроллера

К0607 схематически изображено на рисунке 1.

В контроллер входят следующие

узлы:

- узел сопряжения;

- схема адресации,

позволяющая выбирать нужный блок и регистр в нем;

- регистр статуса

и управления, часть разрядов которого отражает текущее состояние

контроллера, а другие служат для управления шинами магистрали

крейта и режимами работы;

- регистр маски

и запросов, предназначенный для сгруппированных LAM-запросов

от модулей крейта (старший байт) и установки масок (младший

байт);

- 16-разрядный

регистр данных, предназначенный для обмена данными между контроллером

и модулями в крейте;

- 8-разрядный

регистр старшего байта, дополняющий 16-разрядное слово данных

до 24 разрядов;

- схема прерывания,

которая обеспечивает передачу данных о LAM-запросах в компьютер.

Контроллер работает следующим

образом.

В принимаемом узлом сопряжения

последовательном коде выделяются две части: адрес и данные.

Адрес поступает на схему адресации, которая определяет N и

A, а данные поступают в выбранный в соответствии с N и A регистр.

В первую очередь заполняются внутренние регистры контроллера,

которые имеют следующие адреса:

N(0) A(0) -

регистр статуса и управления;

N(0) A(1) -

регистр маски и запросов;

N(0) A(2) -

регистр старшего байта.

После того как

заполнены внутренние регистры, поступает посылка с N0, и схема

адресации инициирует КАМАК-цикл, выставляя на магистраль крейта

то, что лежит во внутренних регистрах контроллера.

1.

Формат внутренних регистров

Статусный регистр:

Разряды F1,

F2, F4, F8, F16 соответствуют шинам F магистрали.

Разряд IF

управляет шиной "Inhibit" на магистрали.

Разряд DE

разрешает (если установлен) или запрещает (если сброшен) прерывания

Разряд D=1,

если имеется хотя бы один немаскированный групповой запрос.

Разряд "C",

если установлен, дает цикл "Clear".

Разряд "Z",

если установлен, дает цикл "Zero".

Разряды "C"

и "Z" автоматически сбрасываются после каждого

цикла.

Разряд XE,

если установлен, разрешает прерывание по отсутствию ответа

от адресуемого модуля.

Разряд IL=1,

если IF=1 либо включен "Inhibit" с передней панели.

Разряды Q,

X содержат соответственно Q и X последнего КАМАК-цикла

и фиксируются по стробу S1.

Прочитав CSR, можно узнать о

наличии группового запроса, состояния шины "Inhibit" и об

ответах по Q и X на последний КАМАК-цикл.

Разряды Q, X, C, Z, IF, DE только

записываются от ЭВМ, а разряды XE, F1, F2, F4, F8, F16 и пишутся

и читаются, следовательно, слово, записанное в CSR, при чтении

выглядит несколько иначе.

Регистр старшего байта (DHR)

имеет следующий формат:

Реально имеется два 8-разрядных

регистра, один из которых только читается (после КАМАК-функции

чтения ), а другой только пишется от ЭВМ (перед функцией записи).

С помощью DHR

производится переформатирование 24-разрядной информации на

КАМАК-магистрали в два слова 16-разрядной ЭВМ. При передаче

24-разрядного слова в регистр КАМАК делается запись старшего

байта в DHR по N(0)A(2), затем, при записи остальных 16 разрядов,

на магистраль автоматически передается содержимое этих 16

разрядов и содержимое DHR - все 24-разрядное слово.

При чтении данных в ЭВМ производится

чтение младших 16 разрядов из КАМАК-устройства, при этом 8

старших разрядов остаются в DHR, который затем можно прочитать

по N(0) A(2).

2. Система

прерываний К0607

Схема обработки

прерываний в К0607 показана на рисунке 2. LAM-запросы от модулей

по индивидуальным проводам поступают в контроллер и собираются

в группы по схеме "или". Таких схем в контроллере восемь.

Соответствие между групповыми запросами Dk и запросами

от модулей Lj определяется перемычками внутри контроллера

и в используемых в практикуме контроллерах является следующим:

Групповой запрос

Dk пропускается или не пропускается в зависимости

от состояния соответствующей маски Mk. При Mk=1

групповой запрос Dk пропускается далее. Состояние

масок и групповых запросов от КАМАК-модулей фиксируется в

контроллере в специальном регистре масок и запросов. Его формат

приведен ниже:

Регистр маски и запросов

Восемь групповых запросов также

собираются по схеме "или" и образуют один "обобщенный" запрос

от всего крейта, состояние которого записывается в бит "D"

статусного регистра контроллера.

Прохождение обобщенного запроса

D блокируется, если в разряд DE (DEMAND ENABLE) статусного

регистра записан "0". Если же DE=1, то возникающий обобщенный

запрос инициирует работу узла сопряжения и в IBM PC уходит

сообщение о наличии в крейте запроса на прерывание.

В соответствии с этим сообщением

интерфейс ППИ (ИПС) устанавливает на шине IRQ IBM PC активное

состояние и в компьютере срабатывает аппаратное прерывание.

Разработка программ обслуживания

прерывания требует специальных средств и более глубокого изучения

работы компьютера. В большинстве простых случаев достаточно

ограничиться работой "по флагу", когда инициатором всех обменов

является компьютер.

Документация и ПО

>>>

|